GIẢI PHÁP MÔ PHỎNG MỤC TIÊU RADAR

Giải pháp Tabor Proteus AWT mô phỏng mục tiêu Radar (RTS) toàn diện: Đơn giản hóa kiến trúc, tối ưu độ chính xác và giảm thiểu độ trễ.

CÁC THÁCH THỨC với hệ thống đo kiểm radar truyền thống

Các kỹ sư thường phải đối mặt với những hạn chế kỹ thuật từ các hệ thống cũ hoặc các thiết bị rời như :

- Vấn đề về độ toàn vẹn của tín hiệu: Các hệ thống DRFM (Digital RF Memory) truyền thống thường sử dụng các bộ điều chế IQ và bộ trộn bên ngoài. Điều này dẫn đến các sai số như lệch pha IQ và nhiễu sóng mang trong băng thông (in-band carrier feed-through), làm giảm độ chính xác của tín hiệu mô phỏng.

- Kiến trúc Phức tạp: Việc kết hợp nhiều thiết bị rời rạc để xây dựng một hệ thống giả lập radar khiến sơ đồ khối trở nên cồng kềnh, khó cấu hình và tốn kém chi phí bảo trì.

- Hạn chế về tốc độ xử lý: Các hệ thống cũ gặp khó khăn trong việc xử lý và biên dịch dữ liệu dạng sóng lớn, gây tốn thời gian.

- Độ trễ: Việc mô phỏng mục tiêu di động yêu cầu khả năng sửa đổi tín hiệu thời gian thực với độ trễ cực thấp để đảm bảo tính trung thực của kịch bản kiểm thử.

Giải pháp MÔ PHỎNG MỤC TIÊU RADAR CỦA TABOR

Giải pháp Tabor Proteus AWT (Arbitrary Waveform Transceiver)

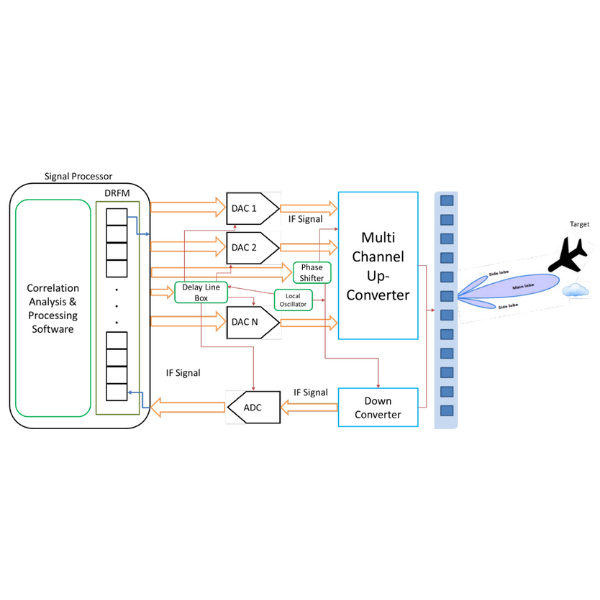

Giải pháp kết hợp Máy phát dạng sóng tùy ý (AWG) và Bộ số hóa (Digitizer) trên cùng một nền tảng FPGA, hoạt động như một hệ thống DRFM tiên tiến nhưng đơn giản hơn nhiều.

- Tạo tín hiệu RF trực tiếp: Proteus sử dụng Bộ dao động điều khiển số (NCO) và bộ nội suy kỹ thuật số tích hợp để tạo tín hiệu RF phức tạp trực tiếp từ thiết bị.

- Kiến trúc All-in-One trên nền tảng FPGA: Proteus tích hợp cả DAC và ADC trong một hệ thống duy nhất được điều khiển bởi FPGA.

- Tốc độ DAC lên tới 9 GSa/s (16-bit) và Digitizer lên tới 5.4 GSa/s (12-bit),Băng thông hỗ trợ phát tín hiệu ở nhiều vùng Nyquist, vươn tới băng tần X-band.

- Trang bị kết nối Thunderbolt 3 và PCIe Gen3, đảm bảo truyền tải dữ liệu cực nhanh.

- Mô phỏng Đa kênh và Beamforming: Hệ thống có thiết kế mô-đun, dễ dàng mở rộng số lượng kênh để tạo ra các hệ thống mô phỏng Mono-Pulse hoặc mảng pha điều khiển điện tử (electronically steered array). Người dùng có thể điều chỉnh pha và biên độ trên từng kênh để mô phỏng hướng sóng đến (TDOA)

Hệ thống Giả lập mục tiêu Radar

Tabor Proteus hoạt động như một hệ thống DRFM. Quy trình hoạt động gồm các bước chính sau:

- Thu tín hiệu: Hệ thống nhận tín hiệu từ Radar cần đo kiểm (RUT), hạ tần từ RF xuống trung tần, sau đó số hóa và giải điều chế để lưu trữ dưới dạng các cặp IQ trong bộ nhớ RAM của FPGA.

- Lưu trữ và Tạo độ trễ: Các mẫu IQ được ghi lần lượt vào bộ nhớ bắt đầu từ địa chỉ đầu tiên. Để mô phỏng một mục tiêu di động, hệ thống tạo ra độ trễ bằng cách đọc dữ liệu từ địa chỉ bộ nhớ cuối cùng ngược về đầu. Số lượng mẫu được đọc sẽ xác định thời gian trễ của xung.

- Phát lại: Tín hiệu sau khi thêm độ trễ sẽ đi qua bộ chuyển đổi số-tương tự (DAC) và được nâng tần lên tần số hoạt động mong muốn. Hệ thống có thể sử dụng nhiều DAC để tạo mô phỏng Mono-Pulse hoặc mảng pha điều khiển điện tử.

Bộ phát sóng (AWG / DAC)

- Hỗ trợ tối đa 4 kênh độc lập

- Tốc độ lấy mẫu DAC lên đến 9 GSa/s

- Độ phân giải DAC 16 bit

- Hỗ trợ chế độ DUC/NCO để chuyển đổi tần số lên (RF up-conversion) trên tất cả các kênh

- Độ lệch thời gian giữa các kênh (channel skew) nhỏ hơn 25 ps

- Hỗ trợ phát trực tiếp (direct streaming) đến DAC

Bộ thu tín hiệu (Digitizer / ADC)

- Lên đến 2 kênh số hoá trên mỗi module

- Tốc độ lấy mẫu ADC lên tới 5.4 GSa/s

- Độ phân giải ADC 12 bit

- Hỗ trợ chế độ DDC (Digital Down-Conversion) để hạ tần RF (down-conversion) trên tất cả các kênh

- Chế độ Loopback, cho phép tín hiệu từ DAC quay lại ADC để thử nghiệm hệ thống khép kín

Hiệu năng DRFM và Mô phỏng Radar

- Độ trễ vòng lặp (loop delay) thấp đến 400 ns

- Kiến trúc cho phép mô phỏng mục tiêu radar (Radar Target Simulation) thời gian thực

- Cho phép xử lý tín hiệu phức tạp bên trong FPGA và đáp ứng tức thì

Khả năng lập trình FPGA

- Tùy chọn FPGA Programming Option để người dùng tự phát triển thuật toán xử lý tín hiệu

- Tùy chọn FPGA Shell Option cho phép tích hợp nhanh các khối IP / thuật toán tùy chỉnh