Quy trình thiết kế và thử nghiệm vi mạch tích hợp bán dẫn (IC) rất phức tạp, đòi hỏi độ chính xác, chuyên môn cao để đáp ứng được các yêu cầu kỹ thuật. Trong đó, việc đo kiểm, xác nhận để đảm bảo thành phẩm IC đã đóng gói đáp ứng được các tiêu chuẩn về độ tin cậy và hiệu suất mong muốn là vô cùng quan trọng.

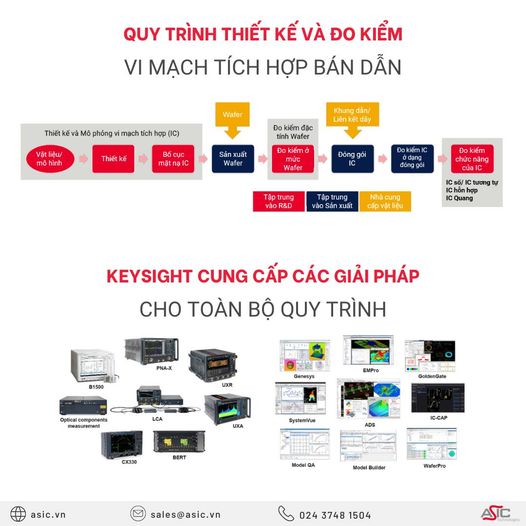

Quy trình thiết kế IC bắt đầu bằng việc mô hình hóa và mô phỏng phần mềm, dựa trên các yêu cầu kỹ thuật đối với IC. Sau đó, thiết kế được khắc lên mặt nạ IC và đặt vào tấm Wafer. Sau khi kiểm tra Wafer, các thành phần được đóng gói và đo kiểm các chức năng để đảm bảo hoạt động chính xác.

Keysight cung cấp các giải pháp phần mềm, thiết bị đo kiểm tiên tiến, tích hợp đồng bộ và hiệu quả, tối ưu cho toàn bộ quy trình, từ thiết kế đến đo kiểm IC.